芯来科技作为中国大陆唯一受邀的RISC-V处理器IP公司在研讨会第一天做了主题演讲,公司首席运营官徐来(Tony Xu) 给出席的嘉宾们分享了国内产业状态、RISC-V在国内当前的发展情况、芯来科技对社区做出了哪些贡献以推动RISC-V在国内生态的发展、以及芯来科技的商用处理器内核。

徐来表示,中国集成电路市场规模和潜力巨大,根据SEMI China,WSTS秋季2018以及ICCAD 2018的数据显示中国大陆地区2018年总集成电路市场规模约834.9亿美金,年复合增长率为22.9%,占2018全球集成电路总市场规模约4016.25亿美金的20.78%, 其中市场规模排名前三位的行业位通讯152.3亿美金,消费类电子89.8亿美金和计算机52.3亿美金。而处理器内核在集成电路产业中无处不在,一方面由于x86和ARM的封闭以及强势,另外一方面由于存量8位和16位处理器市场有向32位处理器转型的需求,而目前市场上除了x86和ARM外,其他处理器架构日渐式微,在这种形势下。

徐来介绍到,目前RISC-V在国内势头正劲,从小众话题成为一个大家关心的话题。上海市政府非常有战略眼光地积极拥抱RISC-V这一趋势,去年便出台了一项为期两年(2018年7月1日-2020年6月30日)针对RISC-V的产业引导政策,并给予RISC-V相关企业经济上的支持。目前已经有企业享受到了该政策所带来的实惠。除了政府支持外,国内相继成立了中国RISC-V产业联盟(CRVIC)和中国开放指令生态(RISC-V)联盟(CRVA)。前者聚焦RISC-V产业落地,后者聚焦开源和开放,两个联盟目前已经达成合作,希望通过产、学、研协同,以加速RISC-V生态在中国的发展和落地。这次活动开始的几天前,台湾也成立了RISC-V产业联盟,该联盟由台湾物联网产业技术协会黄崇仁理事长倡议,力晶、智成、神盾、晶心、联发科、力积电、力旺、嵌议等企业共同发起,以助力台湾产业进入AIoT时代。在联盟成立时邀请了CRVIC理事长戴伟民博士出席并讲话,对于两岸三个产业联盟紧密合作颇为期待。

公司创始人胡振波从2016年便开始进行RISC-V的相关研究,并于2017年创建并维护了中国第一个开源RISC-V处理器项目蜂鸟E203. “蜂鸟虽小五脏俱全”, 蜂鸟E203虽然是一颗面向超低功耗领域的两级流水线的处理器,但具有完备且一流的微架构设计,完整的系统总线和外设接口以及调试接口。该项目完全使用成熟的Verilog HDL写成,RTL编码风格和质量符合工业标准,配套文档完整且通俗易懂,对于想了解RISC-V处理器设计技术人员,以及想了解真正工业级处理器设计风格的工程师和爱好者而言,该项目成为他们的一扇窗口。所以,蜂鸟E203项目一经发布便受到了广泛关注。目前该项目在Github上被Star了627次,Fork了258次,在基金会列举的开源内核项目中被Fork数量排名第二,被Watch数量排名第三,被Star数量排名第四。被广泛地应用于教学、竞赛、企业对RISC-V进行评估、个人研究等目的。

由于对于RISC-V在国内普及所起到的巨大推动作用,蜂鸟E203项目被CRVA联盟授予“科教实践奖”。国外开源社区对中国一直都存在一些刻板印象包括只下载不上传等,徐来表示其实国内有很多个人和公司都在为开源社区做着贡献,来这里分享的一个目的也是改变大家这一刻板印象。

以蜂鸟E203为基础,胡振波于2018年初出版了中国第一本中文RISC-V书籍《手把手教你设计CPU--RISC-V处理器》,并于2019年初出版了中国第二本中文RISC-V书籍《RISC-V架构与嵌入式开发快速入门》,前者到目前已经售出超过8000本,后者超过2000本,做到基本上国内RISC-V 圈子人手一本。此套书籍将晦涩的处理器知识描述得非常通俗易懂,一本处理器设计书籍居然能够与Python编程等热门编程书籍一起成为国内技术畅销书籍实属奇迹。因此胡振波获得了出版社授予的2018年度优秀作者奖。

芯来科技创始团队坚信RISC-V是中国处理器内核IP产业的最后一次机会有感于国内没有一家专业的RISC-V内核IP和解决方案公司,芯来科技创始团队在彼时没有退缩,而是决定更向前再迈一步,成立一家专注AIoT领域的RISC-V处理器商业公司,用实际行动去证明RISC-V能够被用于主流IC公司的量产产品中。目前公司正在不断完善超低功耗产品线,并扩展产品线至中高性能产品并支持矢量指令以满足边缘计算领域的需求。

徐来表示,晶心科技与芯来科技彼此选择成为了合作伙伴,希望结合双方的优势将RISC-V带入到主流市场。N22系列处理器内核便是双方的工程师通力合作的结晶,该处理器内核IP是目前全球市场上最先进的商业RISC-V处理器内核 ● 支持晶心科技RISC-V V5/V5e 延伸指令集,具备最好的PPA指标,性能可超过3.93CoreMark/MHz; 电路门数(Gate Count)可低至约12K(最小可用配置); 频率高达800MHz(worst-case)以及动态功耗可低至2.0 uW/MHz (TSMC 28nm HPC+);

● 采用了最新的快速中断标准,中断响应的实时性大幅提升;

● N22处理器内核IP采用成熟稳健的Verilog HDL语言进行代码编写,具有良好的用户可读性。

● 此外,N22处理器内核配套的AndeSight™ 为专业图形化集成开发环境(IDE,Integrated Development Environment),是目前业界最出色并广为接受使用的专业RISC-V IDE开发工具,现在也提供免费下载服务,让用户优先体验完善的IDE 功能所带来的效率提升。

目前芯来团队正在为N22增加DSP,FPU和ACE的特性,并不断优化电路门数(Gate Count)使其在最小可用配置(带硬件乘除法器)的情况下能够达到约12K的最高业界标准。

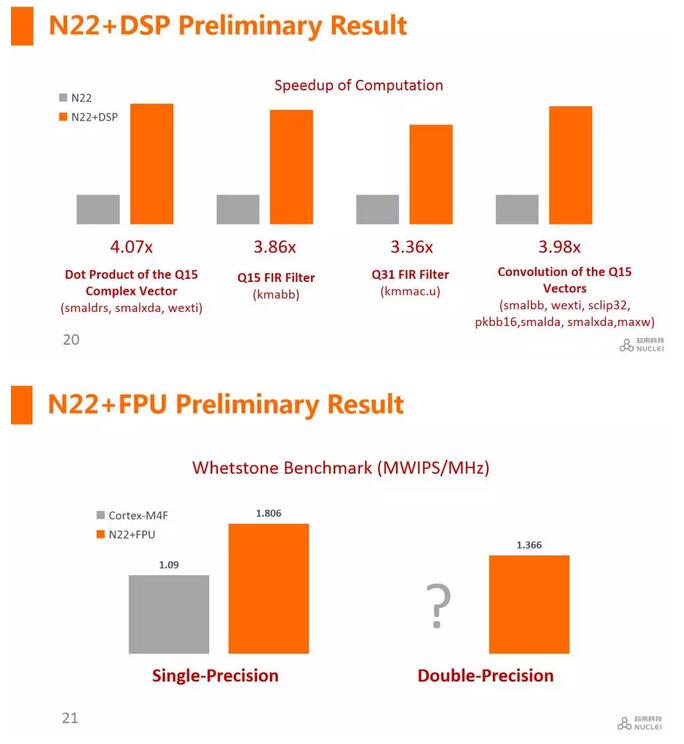

本次分享的最后,徐来也带来了N22的DSP和FPU特性的一些预览数据供大家参考。针对当前研发中的DSP特性,对于Q15复数点积(Dot Product of the Q15 Complex Vector)、 Q15 FIR过滤器(Q15 FIR Filter)、 Q31 FIR过滤器(Q31 FIR Filter)以及Q15向量的卷积(Convolution of the Q15 Vectors)分别带来了比不带DSP特性的N22的4.07、 3.86,、3.36以及3.98倍的运算加速。而对于FPU特性,Whetstone Benchmark目前在单精度的结果为1.806 MWIPS/MHz、双精度的为1.366 MWIPS/MHz, 相比而言,ARM Cortex-M4F在单精度情况下为仅1.09 MWIPS/MHz、而且不支持双精度运算。目前芯来团队正在持续完善和优化这些特性中,相信在正式发布的时候,结果还会有不少提升,值得持续关注。

于此同时,我们希望能够有更多的合作伙伴与我们共建一个更加强大和牢固的RISC-V生态,为本土实现国产自主可控的芯片产业全面赋能。