本土RISC-V CPU IP领军企业——芯来科技正式发布基于RISC-V指令集的高性能商业处理器CPU IP——UX1000系列,为高性能处理器内核提供了RISC-V CPU IP的国产自主选择。

在网络、通信和AI高速发展的时代,下游智能设备的应用对处理器性能和算力需求不断提升。开放标准的RISC-V指令集架构由于其灵活性和扩展性,近年来生态发展速度非常迅猛,在各类应用场景遍地开花,高性能领域也不断在突破。

芯来科技此次全新发布的UX1000系列是拥有多译码宽度、乱序发射与执行能力的64位高性能应用处理器,主要针对网络处理、人工智能、自动驾驶、数据中心加速卡、高性能移动设备等应用,进一步满足了本土当下日益高涨的国产高性能处理器IP需求。

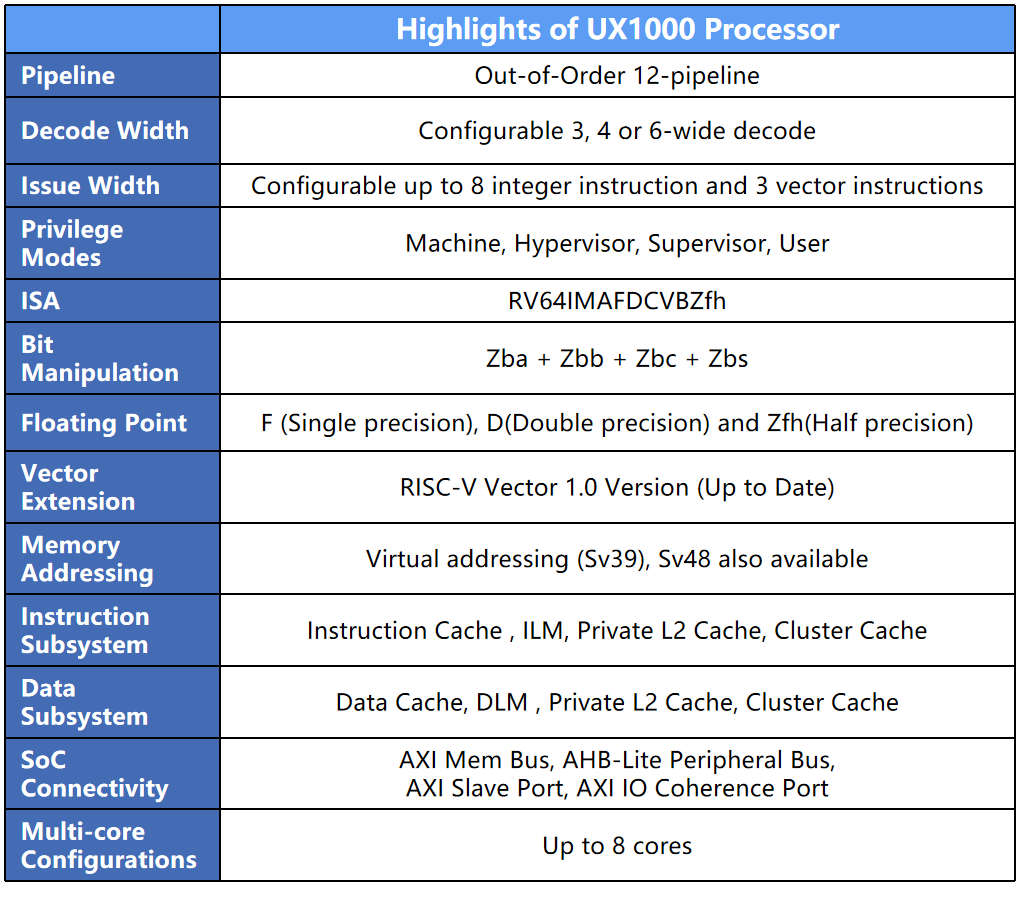

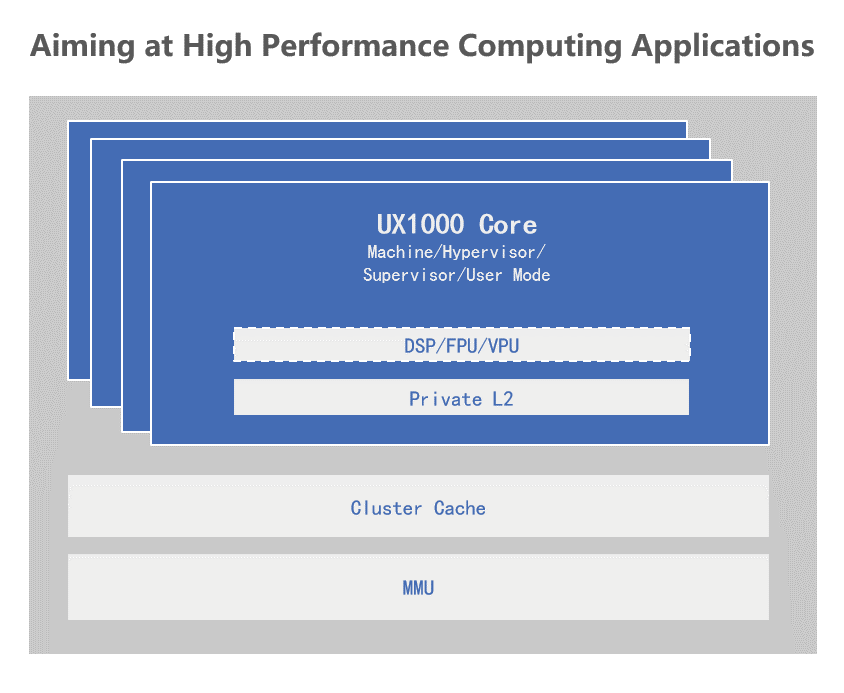

UX1000系列拥有高度可配置的流水线,用户可根据不同性能需求进行选择,为系统设计提供了较强的灵活度:

UX1000系列有三种不同的配置分类:UX1030、UX1040和UX1060

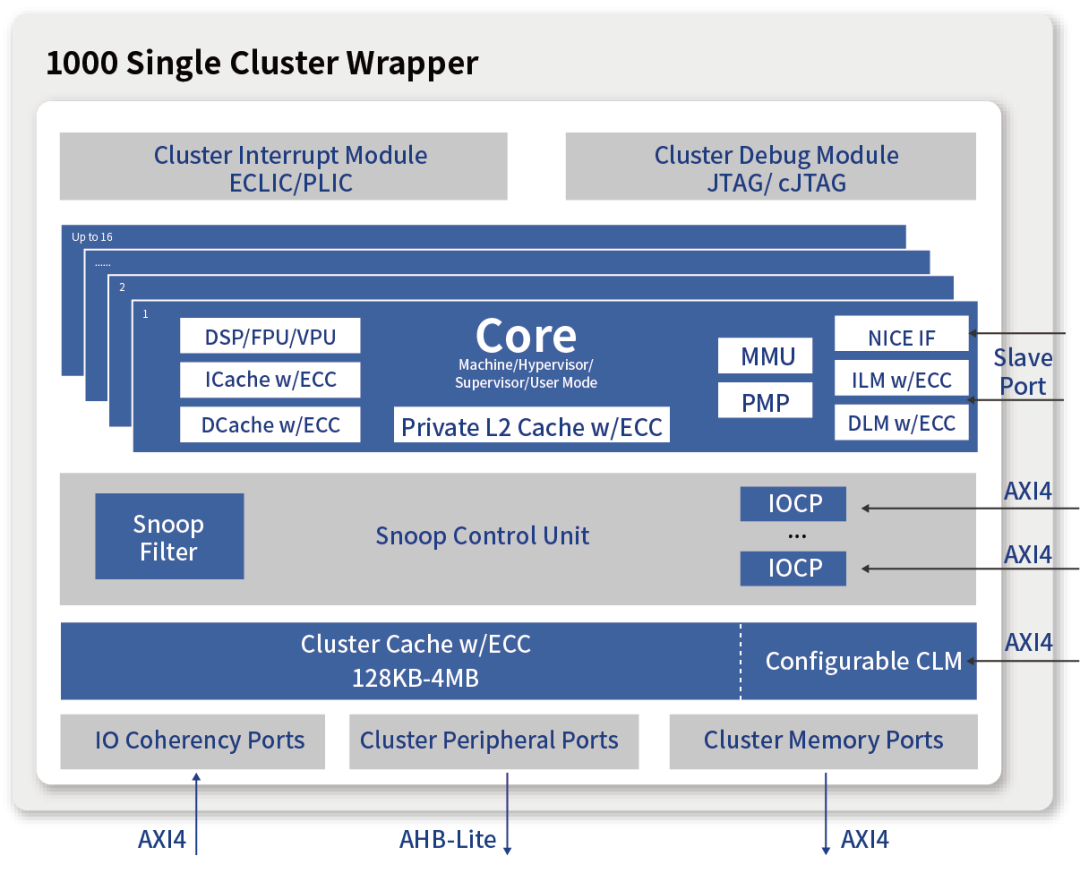

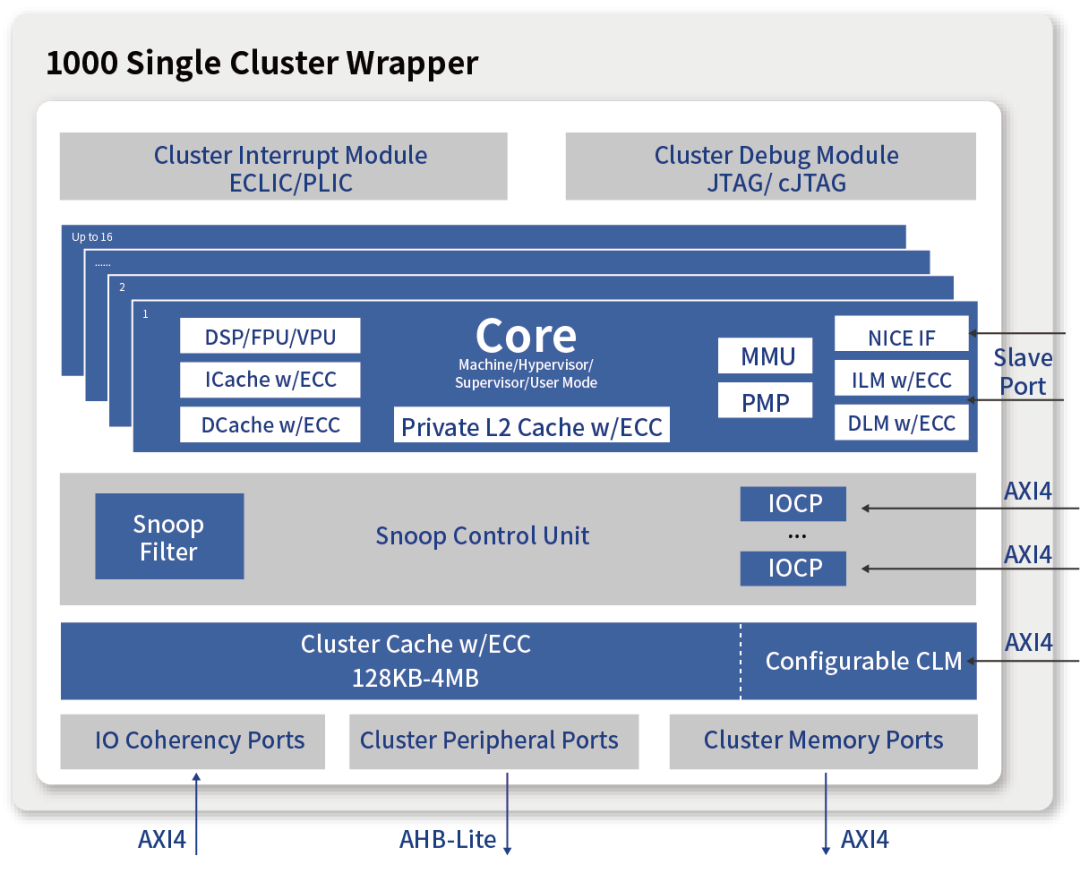

UX1000系列单Cluster支持多种可配特性:

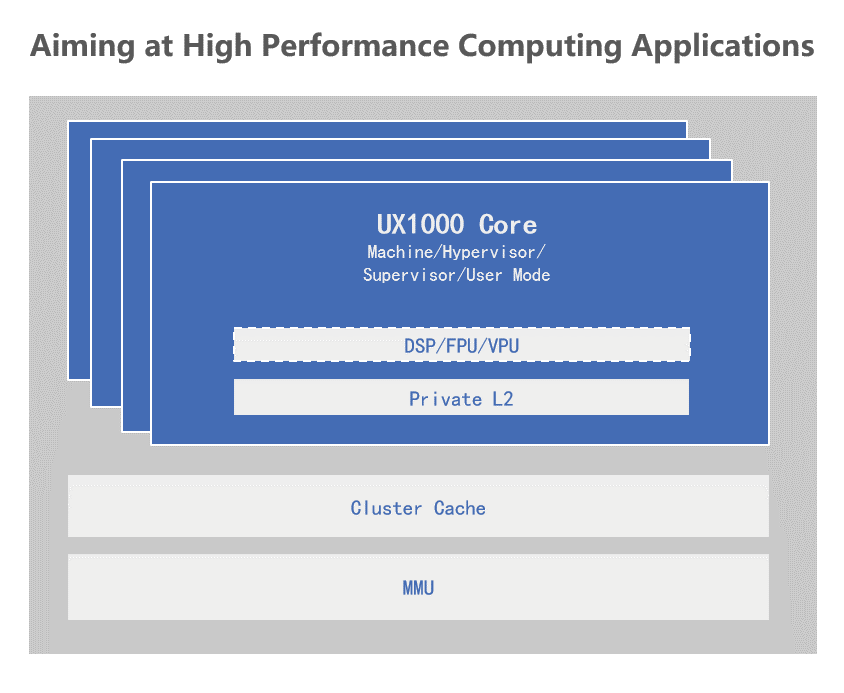

UX1000系列单Cluster可以配置SMP多核,且支持最多3级缓存。

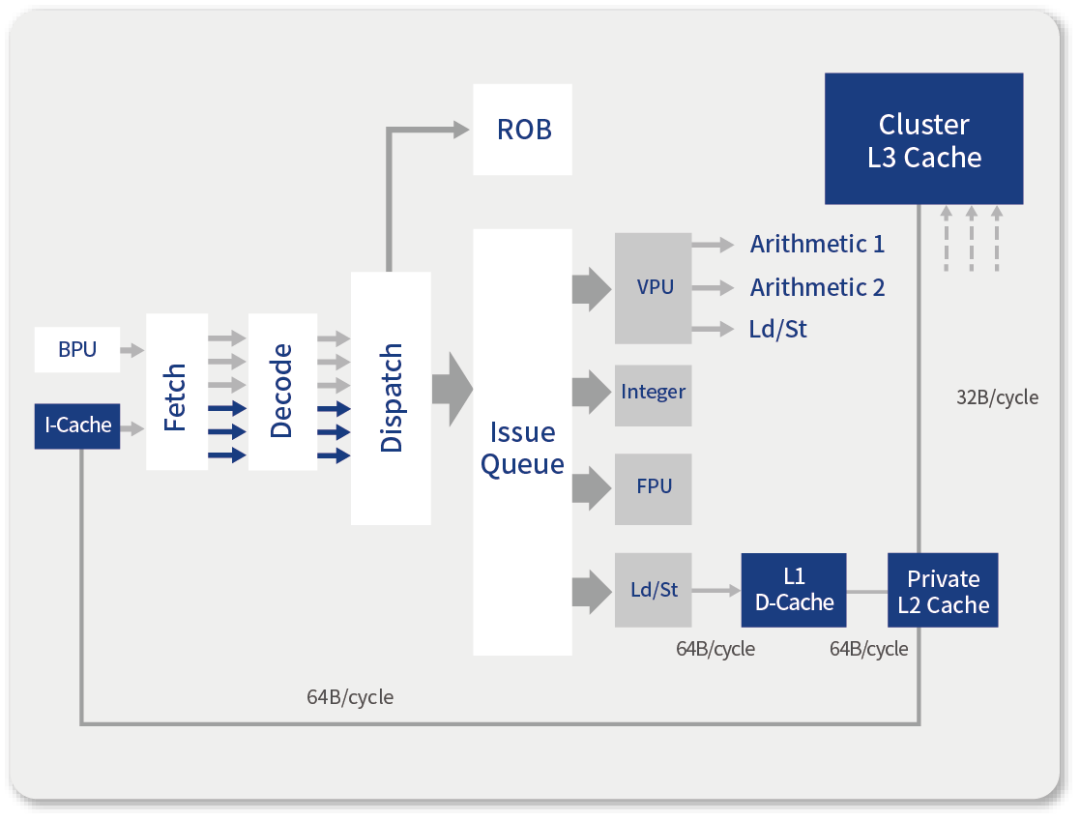

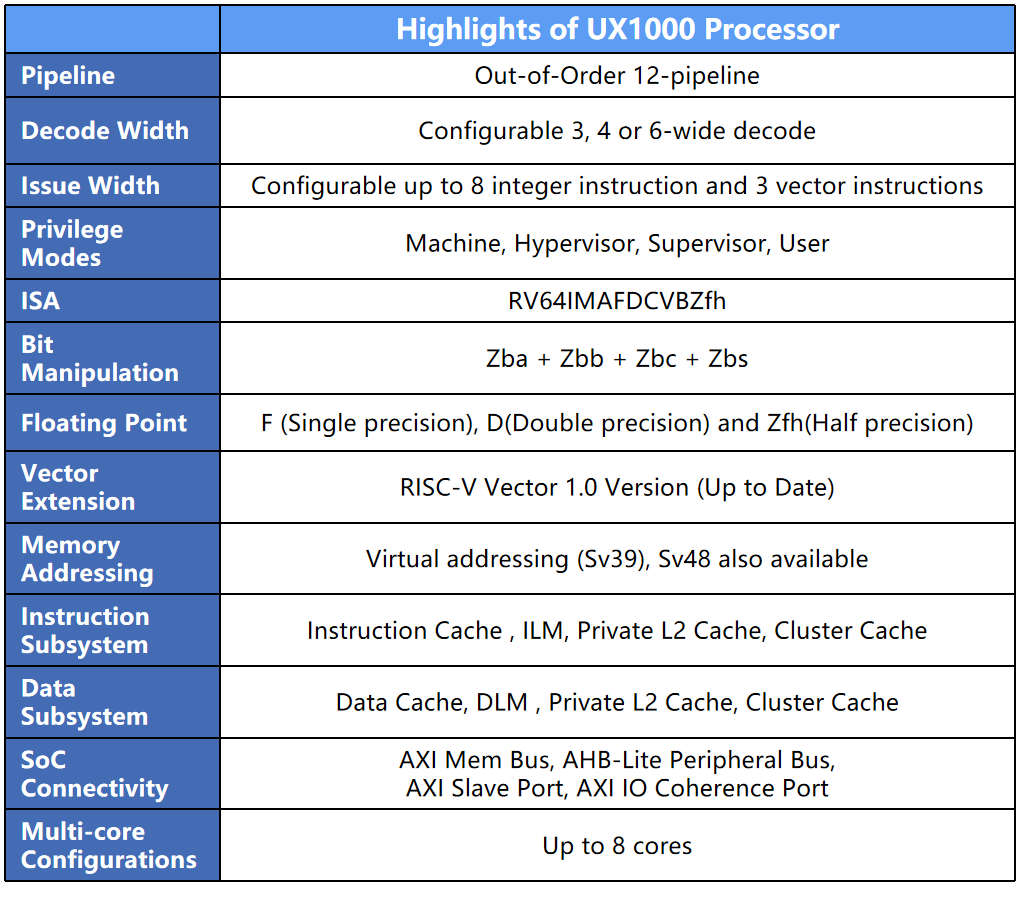

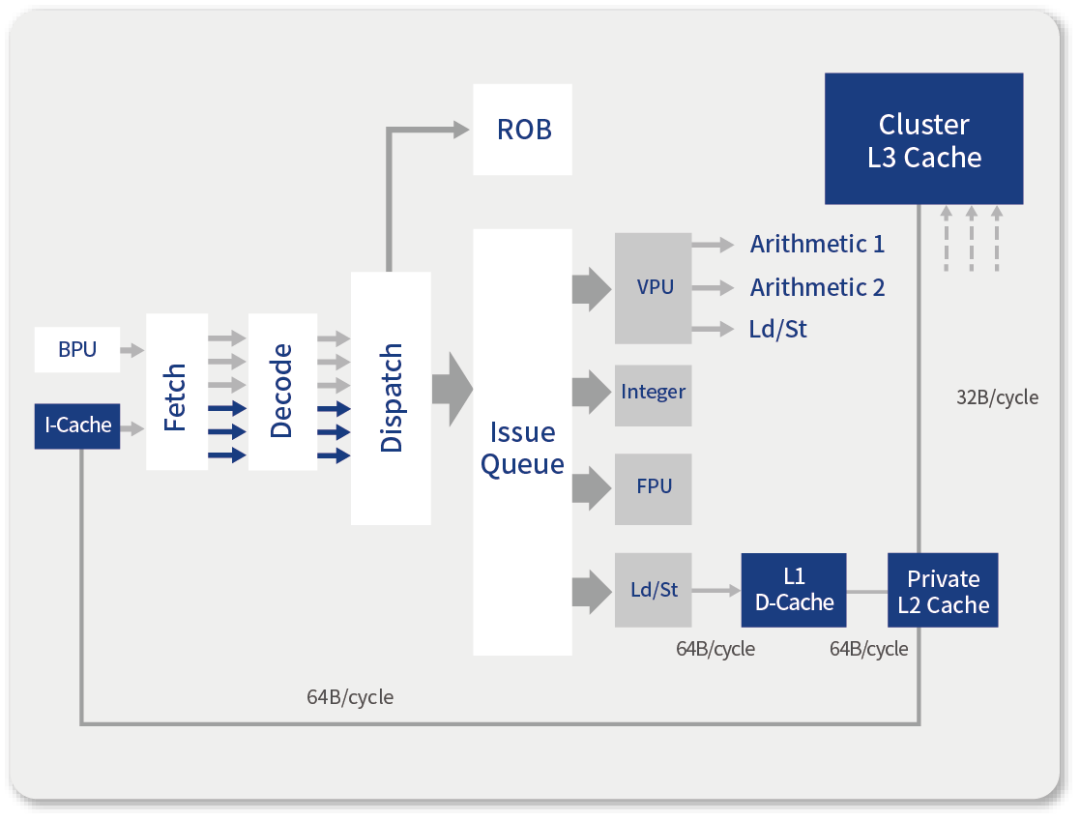

UX1000系列处理器基于RISC-V RV64IMAFDCVBKZfh并严格遵循RISC-V标准指令的12级流水线乱序执行处理器;UX1000具备较强算力,支持每周期最多达10条标量指令和2条矢量指令的发射宽度(Issue Width);可配置的指令与数据缓存(ICache / DCache)与片上SRAM(ILM / DLM)且支持ECC;在内存访问设计上,UX1000支持了私有L2缓存,提供更高效的数据读取存储能力;支持严格按照RISC-V Vector1.0标准的VPU矢量计算单元,拥有2条计算流水线单元和1条数据读写流水线,可配置128b / 256b的VLEN,支持INT8 / 16 / 32 / 64以及BF16 / F16 / F32 / F64数据类型。可配置IO一致性接口(IOCP),在IOCP接口的帮助下,外部Master(例如NPU、加速器、PCIe、DMA等)可以和Core以及Cluster缓存共享数据读取,并保持缓存一致性;

Cluster Cache支持SECDED ECC;

支持将Cluster Cache配置成Cluster Local Memory,并且可以支持CLM接口。

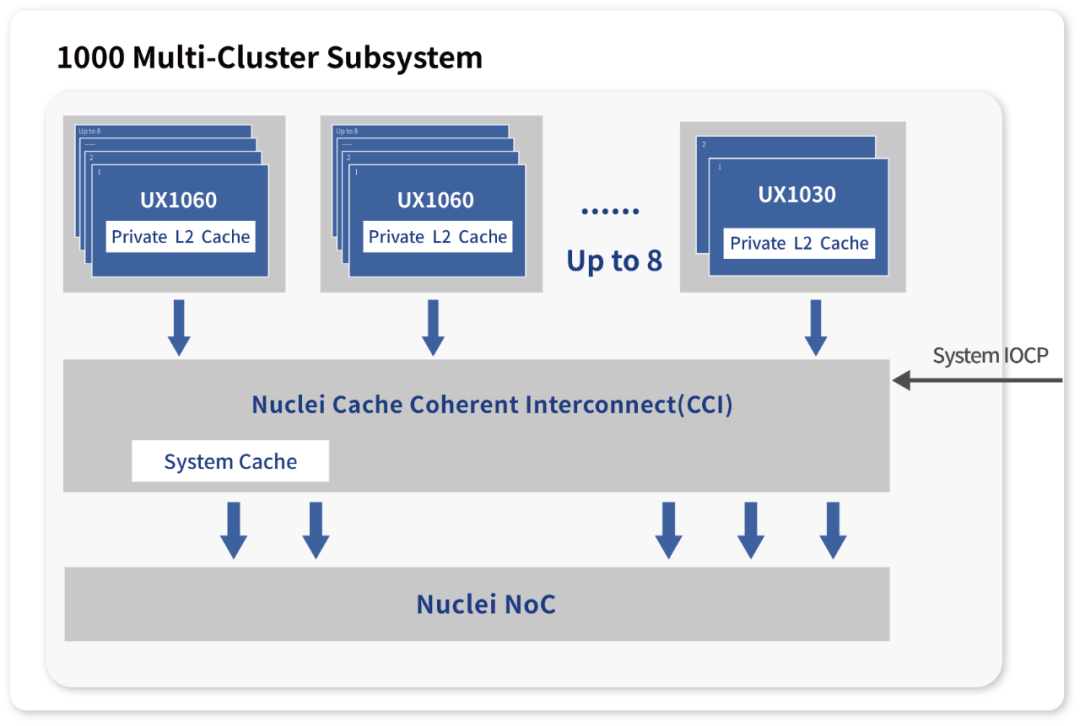

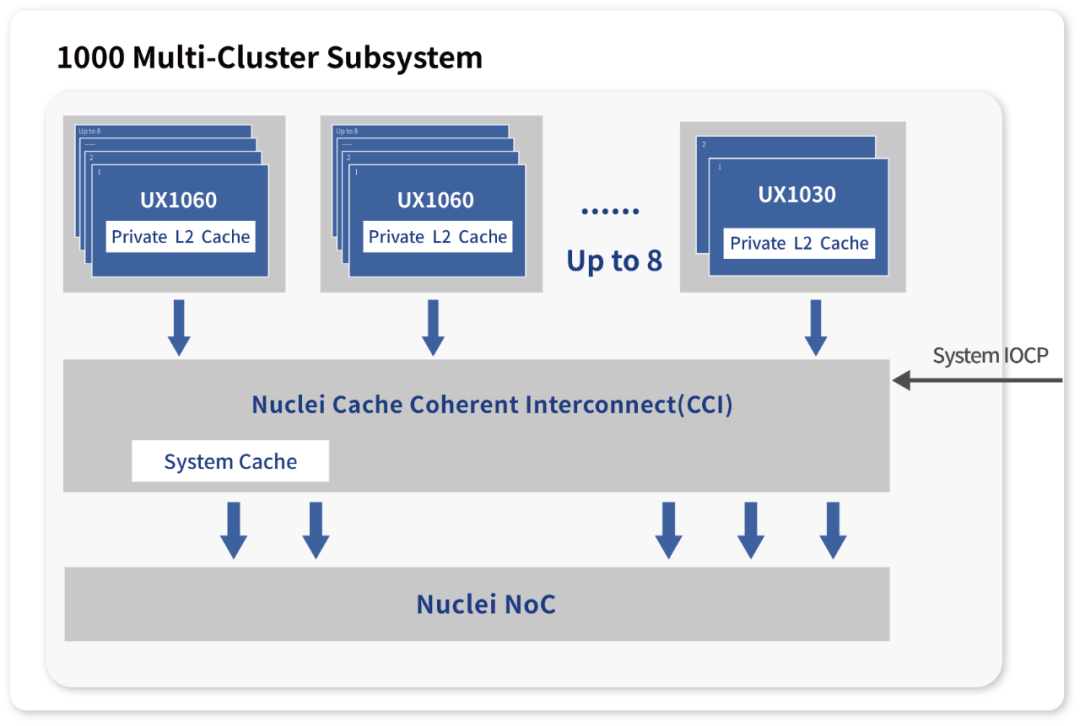

UX1000系列支持多Cluster配置,为高端SoC提供更强大的CPU主控性能。

每个Cluster支持最多8核,每个核都可以单独配置私有L2;Nuclei-CCI:芯来自研的基于Cross-Bar的Coherent总线,应用于Multi-Cluster场景;- 异构多Cluster模式(每个Cluster可以灵活配置不同内核)

- 支持系统级缓存System Cache(L3 Cache)

Nuclei-NoC:芯来自研的基于Mesh-NoC的Non-Coherent总线UX1000的多Cluster系统同样支持IO一致性接口(System-IOCP)

开启乱序高性能篇章,持续推出更多RISC-V CPU IP产品

合抱之木,生于毫末;九层之台,起于垒土。芯来科技自成立以来,相继推出了100、200、300、600、900系列,为本土产业提供了一系列全栈的RISC-V CPU IP解决方案。此次推出的1000系列,进一步开启了乱序高性能CPU的篇章。未来芯来科技将持续加大投入高性能RISC-V CPU IP研发,进一步充实国产RISC-V CPU IP的产品图谱,赋能RISC-V生态在更多高性能应用领域落地,促进RISC-V在中国本土半导体设计产业的蓬勃发展!

芯来科技成立于2018年,一直专注于RISC-V CPU IP及相应平台方案的研发,是本土RISC-V领域的代表性企业。芯来科技从零开始,坚持自研,打造了N/U、NX/UX四大通用CPU IP产品线和NS、NA、NI三个专用CPU IP产品线。其中:

* N/U(支持SV32 MMU)是32位架构,主要用于边缘计算、低功耗和IoT场景;* NX/UX(支持SV39和SV48 MMU)是64位架构,主要用于数据中心、网络安全、存储等高性能应用场景;* NS(Security)面向支付等高安全场景;* NA(Automotive)面向功能安全汽车电子场景;* NI(Intelligence)面向AI等高性能计算场景。目前已有超过200家国内外正式授权客户使用了芯来科技的RISC-V CPU IP,遍及AI、汽车电子、5G通信、网络安全、存储、工业控制、MCU、IoT等多个领域。▼往期精彩回顾▼

芯来正式发布HSM安全子系统方案,进一步拓展RV应用领域